-

This exploded diagram exhibits an extra 64MiB of L3 cache atop the middle of the CCD, with structural silicon inserts to both facet of the brand new layer.

-

AMD teased X3D packaging in its Financial Analyst Day a number of months in the past, however the expertise has reached manufacturing standing rather more shortly than anticipated.

-

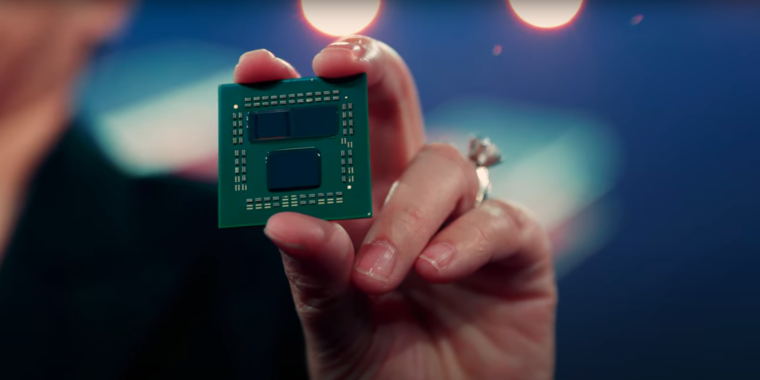

AMD CEO Lisa Su holds up a delidded, 3D-stacked Ryzen 5900x processor on stage at Computex 2021.

Yesterday at Computex 2021, AMD CEO Lisa Su confirmed off the corporate’s subsequent large efficiency play—3D stacked chiplets, permitting the corporate to triple the quantity of L3 cache on its flagship Zen 3 CPUs.

The expertise is simply what it feels like—a layer of SRAM cache sitting atop the Complex Core Die (CCD) of the CPU itself. Current Zen 3 structure integrates 32MiB of L3 cache per eight-core chiplet—making 64MiB whole for a 12- or 16-core chiplet just like the Ryzen 9 5900X or 5950X. The new expertise provides an extra 64MiB L3 cache on high of every chiplet’s CCD, bonded with through-silicon vias (TSVs).

The extra 64MiB L3 cache layer doesn’t prolong the width of the CCD, leading to a necessity for structural silicon to steadiness strain from the CPU cooling system. Compute and cache dies are each thinned within the new design, permitting it to share substrate and warmth spreader expertise with present Ryzen 5000 processors.

-

Gaming workloads profit particularly from extra L3 cache, as demonstrated by the 12% uplift going from 64MiB to 192MiB on this side-by-side demo.

-

Su claimed 15% common gaming efficiency uplift for the brand new expertise.

Tripling the L3 cache on Ryzen 5000 permits efficiency positive aspects beneath some workloads—significantly archive compression/decompression and gaming—much like these seen with total new CPU generations. AMD demonstrated efficiency uplift through a Gears of War 5 demo. Paired with an unspecified GPU and with clock velocity mounted at 4 GHz, a current-model 5900X system achieved 184 fps—whereas the triple-cached prototype managed 206 fps, a acquire of roughly 12 p.c.

AMD claims a mean of 15 p.c improved gaming efficiency with the brand new expertise, starting from a low of 4 p.c for League of Legends to a excessive of 25 p.c for Monster Hunter: World. This efficiency enchancment requires neither smaller course of node nor elevated clock velocity—which is very fascinating, in an period the place clock speeds have largely hit a wall, and a physics-determined finish to process-node shrink appears to be on the horizon as properly.

Anandtech’s Ian Cutress notes that AMD’s new 3D chiplet stacking course of is clearly TSMC’s SoIC Chip-on-Wafer technology in motion. While AMD is—at the least thus far—limiting itself to 2 layers, TSMC has demonstrated a full 12 layers in motion. The downside right here is thermal—including RAM is a near-ideal use of the expertise, for the reason that extra silicon does not generate a lot in the best way of extra warmth. Stacking CPU on CPU can be much more problematic.

AMD states that the redesigned 5900X will enter manufacturing later this 12 months—properly earlier than Zen 4’s scheduled launch in 2022. For now, AMD is specializing in the brand new expertise for “high-end Ryzen” CPUs solely—no point out was made from Epyc, and the extra silicon required for the added cache makes it a possible nonstarter for funds processors, given present supplies shortages.

Listing picture by AMD

/cdn.vox-cdn.com/uploads/chorus_asset/file/25663594/Screenshot_2024_10_07_at_4.37.09_PM.png)

/cdn.vox-cdn.com/uploads/chorus_asset/file/25047547/236883_Epic_Vs_Google_B_CVirginia.jpg)

/cdn.vox-cdn.com/uploads/chorus_asset/file/24828467/Installer_Site_Post_01.jpg)

/cdn.vox-cdn.com/uploads/chorus_asset/file/25264233/Circle_to_search.png)

/cdn.vox-cdn.com/uploads/chorus_asset/file/25253483/DSC06441.jpg)